##

### Doc vs Internet

| 78.82% Originality | 21.18% Similarity | 176 Sources |  |

|--------------------|-------------------|-------------|--|

|                    |                   |             |  |

### Web sources: 171 sources found

| 1. http://www.freepatentsonline.com/9799557.html                                                    | 8.67% |

|-----------------------------------------------------------------------------------------------------|-------|

| 2. https://patents.google.com/patent/US9324780B2/en                                                 | 8.07% |

| 3. https://patents.justia.com/patent/10074547                                                       | 7.44% |

| 4. http://www.freepatentsonline.com/10008463.html                                                   | 4.84% |

| 5. https://patents.google.com/patent/US20170301611A1/en                                             | 4.66% |

| 6. https://patents.justia.com/patent/9177797                                                        | 3.83% |

| 7. https://patents.google.com/patent/US20140263959A1/en                                             | 3.81% |

| 8. https://patents.google.com/patent/US7898037B2/en                                                 | 3.75% |

| 9. http://www.freepatentsonline.com/y2015/0050779.html                                              | 3.63% |

| 10. https://patents.justia.com/patent/9324752                                                       | 3.51% |

| 11. https://patents.justia.com/patent/20180374884                                                   | 3.47% |

| 12. https://patents.justia.com/patent/20170364071                                                   | 3.15% |

| 13. https://patents.google.com/patent/US20170021161A1/en                                            | 3.11% |

| 14. https://patents.google.com/patent/US8390089B2/en                                                | 3.11% |

| 15. https://patents.justia.com/patent/20190137883                                                   | 3.09% |

| 16. https://patents.justia.com/patent/9601430                                                       | 3.07% |

| 17. http://www.freepatentsonline.com/6621138.html                                                   | 2.92% |

| 18. https://patents.google.com/patent/US8951864B2/en                                                | 2.92% |

| 19. https://patents.justia.com/patent/9147377                                                       | 2.92% |

| 20. https://patents.google.com/patent/US7860222B1/en                                                | 2.82% |

| 21. https://patents.google.com/patent/US8190264B2/en                                                | 2.78% |

| 22. https://patents.google.com/patent/US7653433B2/en                                                | 2.78% |

| 23. https://patents.justia.com/patent/9530776                                                       | 2.54% |

| 24. https://www.sparrho.com/item/systems-methods-and-media-for-providing-visual-indication-of-a-bla | 2.5%  |

| 25. http://www.freepatentsonline.com/y2013/0099282.html                                             | 2.42% |

| 26. https://patents.google.com/patent/US20170271460A1/en                                            | 2.38% |

| 27. http://www.patentsencyclopedia.com/app/20150357466                                              | 2.28% |

| 28. http://www.freepatentsonline.com/y2019/0067124.html                                             | 2.14% |

| 29. https://patents.justia.com/patent/20180174831                                                   | 2.1%  |

| 30. http://www.freepatentsonline.com/y2017/0170027.html                                             | 2.06% |

| 31. http://www.freepatentsonline.com/y2018/0033693.html                                             | 1.98% |

| 32. http://www.freepatentsonline.com/y2017/0229372.html                                             | 1.98% |

| 33. http://www.freepatentsonline.com/y2017/0092495.html                                             | 1.98% |

| 34. http://www.freepatentsonline.com/y2016/0013059.html                                             | 1.98% |

|                                                                                                     |       |

Similarity

Similarity from a chosen source

US20180175215A1 Uploaded: 05/13/2019 Checked: 05/13/2019

| 5. http://www.freepatentsonline.com/y2017/0227851.html          | 1.9%  |

|-----------------------------------------------------------------|-------|

| 6. https://patents.google.com/patent/US20160027874A1/en         | 1.75% |

| 7. https://patents.google.com/patent/US20090100041A1/en         | 1.73% |

| 8. https://patents.justia.com/patent/20170025313                | 1.59% |

| 9. https://patents.google.com/patent/US20060065891A1/en         | 1.57% |

| 0. https://patents.justia.com/patent/9721896                    | 1.49% |

| 1. http://www.freepatentsonline.com/y2013/0026622.html          | 1.13% |

| 2. http://www.patentsencyclopedia.com/class/000475407           | 0.97% |

| 3. http://www.freshpatents.com/-dt20170921ptan20170271205.php   | 0.95% |

| 4. https://patents.google.com/patent/USRE43528E1/en             | 0.95% |

| 5. https://patents.google.com/patent/US8890224B2/en             | 0.89% |

| 6. https://www.freshpatents.com/-dt20160929ptan20160283259.php  | 0.85% |

| 7. https://www.lens.org/lens/patent/US_2008_0108797_A1/fulltext | 0.61% |

| 8. http://www.freepatentsonline.com/y2017/0097875.html          | 0.56% |

| 9. https://patents.google.com/patent/US7453498B2/en             | 0.48% |

| 0. http://www.freepatentsonline.com/9369083.html                | 0.48% |

| 1. https://patents.google.com/patent/US20040110119A1/en         | 0.48% |

| 2. https://patents.google.com/patent/US9413448B2/en             | 0.46% |

| 3. https://www.lens.org/lens/patent/US_2006_0062866_A1/fulltext | 0.42% |

| 4. https://patents.google.com/patent/US8261058B2/en             | 0.42% |

| 5. https://patents.google.com/patent/US20140137257A1/en         | 0.42% |

| 6. http://www.freepatentsonline.com/y2015/0221720.html          | 0.4%  |

| 7. https://patents.google.com/patent/US8600895B2/en             | 0.38% |

| 8. https://patents.google.com/patent/WO2002005061A2/en          | 0.38% |

| 9. https://patents.google.com/patent/US9557723B2/en             | 0.38% |

| 0. https://patents.google.com/patent/US20040148370A1/en         | 0.38% |

| 1. https://patents.google.com/patent/US8090817B2/en             | 0.38% |

| 2. https://patents.google.com/patent/US8452108B2/en             | 0.38% |

| 3. https://patents.google.com/patent/US8031630B2/en             | 0.38% |

| 4. https://patents.google.com/patent/US5799286A/en              | 0.36% |

| 5. https://patents.google.com/patent/US8498941B2/en             | 0.36% |

| 6. https://patents.google.com/patent/US8762243B2/en             | 0.34% |

| 7. https://patents.google.com/patent/US20040015329A1/en         | 0.34% |

| 8. https://patents.google.com/patent/US6578147B1/en             | 0.34% |

| 9. https://patents.google.com/patent/US20040088177A1/en         | 0.34% |

| 0. http://www.freepatentsonline.com/7700453.html                | 0.32% |

| 1. https://patents.google.com/patent/US9318651B2/en             | 0.32% |

| 2. https://patents.google.com/patent/US6120460A/en              | 0.32% |

| 3. https://patents.google.com/patent/EP2903204A1/en             | 0.32% |

| 4. https://patents.google.com/patent/US7344736B2/en             | 0.32% |

| 5. http://www.patentsencyclopedia.com/class/000528443           | 0.32% |

| 6. http://www.patentsencyclopedia.com/class/000528080           | 0.32% |

| 7. https://www.lens.org/lens/patent/US_2012_0273945_A1/fulltext | 0.26% |

| 8. https://patents.google.com/patent/US8234200B2/en             | 0.24% |

| 9. https://patents.google.com/patent/CA2384791A1/en             | 0.22% |

| 0. https://patents.google.com/patent/US20060166738A1/en         | 0.22% |

| 31. https://patents.google.com/patent/EP1761841A2/en                                       | 0.22 |

|--------------------------------------------------------------------------------------------|------|

| 32. https://patents.google.com/patent/CA2798750A1/en                                       | 0.22 |

| 33. https://patents.google.com/patent/US5966715A/en                                        | 0.22 |

| 34. http://www.freepatentsonline.com/y2018/0001184.html                                    | 0.2  |

| 35. https://www.marketscreener.com/JAPAN-DISPLAY-INC-16043763/news/Japan-Patent-Issued-for | 0.2  |

| 6. https://patents.google.com/patent/US20100012992A1/en                                    | 0.2  |

| 7. http://www.freepatentsonline.com/7979762.html                                           | 0.2  |

| 8. https://patents.google.com/patent/US6691151B1/en                                        | 0.2  |

| 9. https://patents.google.com/patent/WO2012116309A2/en                                     | 0.2  |

| 0. https://patents.google.com/patent/WO2009064451A1/en                                     | 0.2  |

| 1. https://patents.google.com/patent/US20030144680A1/en                                    | 0.18 |

| 2. https://patents.google.com/patent/US20070258329A1/en                                    | 0.18 |

| 3. https://patents.google.com/patent/US20070180509A1/en                                    | 0.18 |

| 4. https://patents.google.com/patent/US20100278453A1/en                                    | 0.18 |

| 5. https://patents.google.com/patent/US20140230314A1/en                                    | 0.18 |

| 6. https://patents.google.com/patent/EP2411953A1/en                                        | 0.18 |

| 7. http://www.freepatentsonline.com/y2016/0110549.html                                     | 0.18 |

| 8. https://patents.google.com/patent/US7490085B2/en                                        | 0.18 |

| 9. https://patents.google.com/patent/US20070106126A1/en                                    | 0.18 |

| 00. https://patents.google.com/patent/US20080281766A1/en                                   | 0.18 |

| 01. https://patents.google.com/patent/US20160359680A1/en                                   | 0.18 |

| 02. https://patents.google.com/patent/US20080243750A1/en                                   | 0.18 |

| 03. https://patents.google.com/patent/US6088659A/en                                        | 0.18 |

| 04. https://patents.google.com/patent/US20090164397A1/en                                   | 0.18 |

| 05. https://patents.google.com/patent/US20080256008A1/en                                   | 0.18 |

| 06. https://patents.google.com/patent/US20090234788A1/en                                   | 0.18 |

| 07. https://patents.google.com/patent/US20090187499A1/en                                   | 0.18 |

| 08. http://www.freepatentsonline.com/8288788.html                                          | 0.16 |

| 09. http://www.freepatentsonline.com/7214615.html                                          | 0.16 |

| 10. http://www.freepatentsonline.com/8143159.html                                          | 0.16 |

| 11. https://patents.google.com/patent/US6770944B2/en                                       | 0.16 |

| 12. http://www.freepatentsonline.com/9577044.html                                          | 0.16 |

| 13. https://patents.google.com/patent/US20020107901A1/en                                   | 0.16 |

| 14. http://www.freepatentsonline.com/y2017/0373142.html                                    | 0.16 |

| 15. https://patents.google.com/patent/WO2014110280A2/en                                    | 0.16 |

| 16. https://patents.google.com/patent/WO2008016694A2/en                                    | 0.16 |

| 17. http://www.patentsencyclopedia.com/app/20140314721                                     | 0.16 |

| 8. https://patents.google.com/patent/WO2006089426A1/en                                     | 0.16 |

| 19. https://patents.google.com/patent/WO2010124184A2/en                                    | 0.16 |

| 20. http://www.patents.com/us-6891271.html                                                 | 0.16 |

| 21. https://patents.justia.com/patent/6580121                                              | 0.16 |

| 22. https://patents.google.com/patent/US8300798B1/en                                       | 0.16 |

| 23. http://www.freepatentsonline.com/y2014/0001514.html                                    | 0.16 |

| 24. http://www.patents.com/us-7148527.html                                                 | 0.16 |

| 25. http://www.freshpatents.com/Alexander-Kalnitsky-SanFrancisco-invdirk.php               | 0.16 |

| 26. https://www.uspto.gov/patents-getting-started/general-information-concerning-patents   | 0.16 |

| 127. http://www.uspto.gov/web/offices/pac/mpep/s608.html                         | 0.16% |

|----------------------------------------------------------------------------------|-------|

| 128. https://patents.google.com/patent/US20140297301A1/en                        | 0.16% |

| 129. https://patents.google.com/patent/US20110301982A1/en                        | 0.16% |

| 130. https://patents.google.com/patent/WO2014143729A1/en                         | 0.16% |

| 131. https://patents.google.com/patent/US20040122719A1/en                        | 0.16% |

| 132. https://patents.google.com/patent/US6219586B1/en                            | 0.16% |

| 133. https://patents.google.com/patent/WO2006044904A2/en                         | 0.16% |

| 134. https://patents.google.com/patent/WO2014146135A2/en                         | 0.16% |

| 135. https://patents.google.com/patent/US20160002680A1/en                        | 0.16% |

| 136. https://patents.google.com/patent/WO2007030633A2/en                         | 0.16% |

| 137. https://patents.google.com/patent/US9477737B1/en                            | 0.16% |

| 138. https://patents.google.com/patent/WO2006074550A1/en                         | 0.16% |

| 139. https://patents.google.com/patent/US20140242199A1/en                        | 0.16% |

| 140. https://patents.google.com/patent/US8928265B2/en                            | 0.16% |

| 141. https://tgs.freshpatents.com/Copper-bxc.php                                 | 0.16% |

| 142. https://patents.google.com/patent/US5555403A/en                             | 0.16% |

| 143. https://www.findlegalforms.com/product/prenuptial-agreement-same-sex-couple | 0.16% |

| 144. https://patents.google.com/patent/US20100332373A1/en                        | 0.16% |

| 145. https://patents.google.com/patent/WO2005078605A1/en                         | 0.16% |

| 146. https://patents.google.com/patent/US20120141448A1/en                        | 0.16% |

| 147. https://patents.google.com/patent/US20080193373A1/en                        | 0.16% |

| 148. https://patents.google.com/patent/US7541935B2/en                            | 0.16% |

| 149. https://patents.google.com/patent/US20170055896A1/en                        | 0.16% |

| 150. https://patents.google.com/patent/WO2011056688A2/en                         | 0.16% |

| 151. https://patents.google.com/patent/US20050283054A1/en                        | 0.16% |

| 152. https://patents.google.com/patent/US7938796B2/en                            | 0.16% |

| 153. http://www.freepatentsonline.com/2476206.html                               | 0.16% |

| 154. https://patents.google.com/patent/US20090089630A1/en                        | 0.16% |

| 155. https://patents.google.com/patent/US7702918B2/en                            | 0.16% |

| 156. https://patents.google.com/patent/US8818753B2/en                            | 0.16% |

| 157. https://patents.google.com/patent/US7601123B2/en                            | 0.16% |

| 158. https://patents.google.com/patent/US5407153A/en                             | 0.16% |

| 159. https://patents.google.com/patent/WO2015116344A1/en                         | 0.16% |

| 160. https://patents.google.com/patent/WO2012071283A1/en                         | 0.16% |

| 161. https://patents.google.com/patent/US6801909B2/en                            | 0.16% |

| 162. https://patents.google.com/patent/US8417311B2/en                            | 0.16% |

| 163. https://patents.google.com/patent/US8367701B2/en                            | 0.16% |

| 164. https://patents.google.com/patent/WO2011103424A2/en                         | 0.16% |

| 165. http://www.freepatentsonline.com/y2009/0198050.html                         | 0.16% |

| 166. http://www.patentsencyclopedia.com/app/20120254842                          | 0.16% |

| 167. https://patents.justia.com/patent/20040028612                               | 0.16% |

| 168. http://www.freepatentsonline.com/y2013/0289802.html                         | 0.16% |

| 169. https://patents.google.com/patent/US20120115581A1/en                        | 0.16% |

| 170. http://www.freepatentsonline.com/y2012/0183535.html                         | 0.16% |

| 171. https://patents.google.com/patent/US8738396B2/en                            | 0.16% |

US20180175215A1 Uploaded: 05/13/2019 Checked: 05/13/2019

81.4%

75.82%

7.6%

4.84%

4.84%

### Web omitted sources: 5 sources found

- 1. https://patents.justia.com/patent/20180175215

- 2. http://www.patentsencyclopedia.com/app/20160064573

- 3. https://patents.justia.com/inventor/priyono-tri-sulistyanto

- 4. http://www.freepatentsonline.com/y2017/0271386.html

- 5. http://www.freepatentsonline.com/y2013/0239077.html

###

|                                                                     | ublication (11) Pub.Nc.: US 2018/0175215 A1                                                                                                                                              |

|---------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                     | (4) 1 up. pare. Jun. 21, 2018                                                                                                                                                            |

| 54) SEMICONDUCTOR DEVICE INCL                                       | UDING Publication Classification                                                                                                                                                         |

| ZENER DIODE AND METHOD OF<br>MANUFACTURING THEREOF                  | (51) Int. Cl.                                                                                                                                                                            |

| 71) Applicant: Vanguard International                               | H01L 29/866 (2006.01)<br>H01L 29/66 (2006.01)                                                                                                                                            |

| Semiconductor Corporation                                           | <b>bn</b> , Hsinchu $\frac{H01L \ 29/06}{H01L \ 29/20}$ (2006.01)<br>(2006.01)                                                                                                           |

| (TW)                                                                | (52) U.S. Cl.<br>CPC <i>H01L 29/866</i> (2013.01); <i>H01L 29/66204</i>                                                                                                                  |

| 72) Inventors: Privono Tri SULISTVANT<br>Yogyakkatta (ID): Manoi KI | (2013.01); <i>H01L 29/2003</i> (2013.01); <i>H01L</i>                                                                                                                                    |

| <b>Dhanbad (IN</b> ): Chia - Hao, I<br>Tainei City (TW): Chih Che   | rng I.TAO,                                                                                                                                                                               |

| Jhudona Township ((TW ); S<br>TU , Jhubei City ((TW))               | hang-Hui' (57) ABSIRACI                                                                                                                                                                  |

| 73) Assignee: Vanguard International                                | A semiconductor device, including an insulator formed on<br>top surface of a semiconductor substrate, a semiconductor<br>layer, contactining a first region of a first conductivity type |

| Semiconductor Corporation                                           | n, Historiu formed on the insulator layer, wherein the first region is a P-                                                                                                              |

| (TW)                                                                | region or an N+ region, a second region of a second<br>conductivity type in direct contact with the first region and                                                                     |

| 21) Appl. No.: 15/896,541                                           | forming a P-N junction with the first region, wherein the P-N<br>junction comprises a first portion parallel to the top surface                                                          |

| 22) Filed: Feb. 14, 2018                                            | of the semiconductor substrate, and the second region is the                                                                                                                             |

| Related U.S. Application Data                                       | semiconductor substrate and partially covered by the semi-<br>conductor laye. a first metallization region in electrica                                                                  |

|                                                                     | ,365, filed on contact with the first region and a second metallization                                                                                                                  |

**abc** Possible character replacement

**abc** Possible character replacement

US20180175215A1 Uploaded: 05/13/2019 Checked: 05/13/2019

**abc** Possible character replacement

#### US 2018/0175215 A1

#### SEMICONDUCTOR DEVICE UNCLUDING ZENER DIODE AND METHOD OF MANUFACTURING THEREOF

1

#### CROSS-REFERENCE TO RELATED APPLICATIONS

[0001] This application is a Continuation of U.S. applicauon ser. No. 14/473,365 illed on Auts. 29, 2014 the entire contrarts of which is berefix expressly incorporated by reference into the present application.

#### BACKGROUND

[0002] Zener diodes are widely used, in applications including resultiers and voltage regulators, for protecting other seniconductor devices from suffering from an undesired pulse. When a zener diode is reverse-biased, it has the ability to hold thevoltage on a certain value, thereby having volltage-stabilizing characteristics.

[0003] Zener diodes are also widely used trimming techniques, which are used to make adjustments to an integrated circuit after fabrication. Triunning techniques typically include laser tripming of thin-film resistors and "zener zap atti-fuse ttriuming. Zener zap triuming has galned wide acceptance because it is field programmable and is less costily to iinplement. The zener zap metihod uses zener diodes having a low to moderate breakdown voltage as trim devices. Typically, a trim circuit includes a string of zener diodes and a string of corresponding resistive elements where each zener diode is connected in parallel to one of the resistive elements. Zener diodes are biased so that they behave as an open circuit as Ifabricated. When trimming is performed, the zener diode is zapped and the junction is short-nironitad. By shorting out selective zener diodes and the associated resistive elements, a desired change in resis tance can be obtained.

#### BRIEF DESCRIPTION OF THE DRAWINGS

[0004] For a more complete understanding of the embodiments, and the advantages thereof reference is now made to the ifollowing descriptions taken in conjunction with the accompanying drawings.

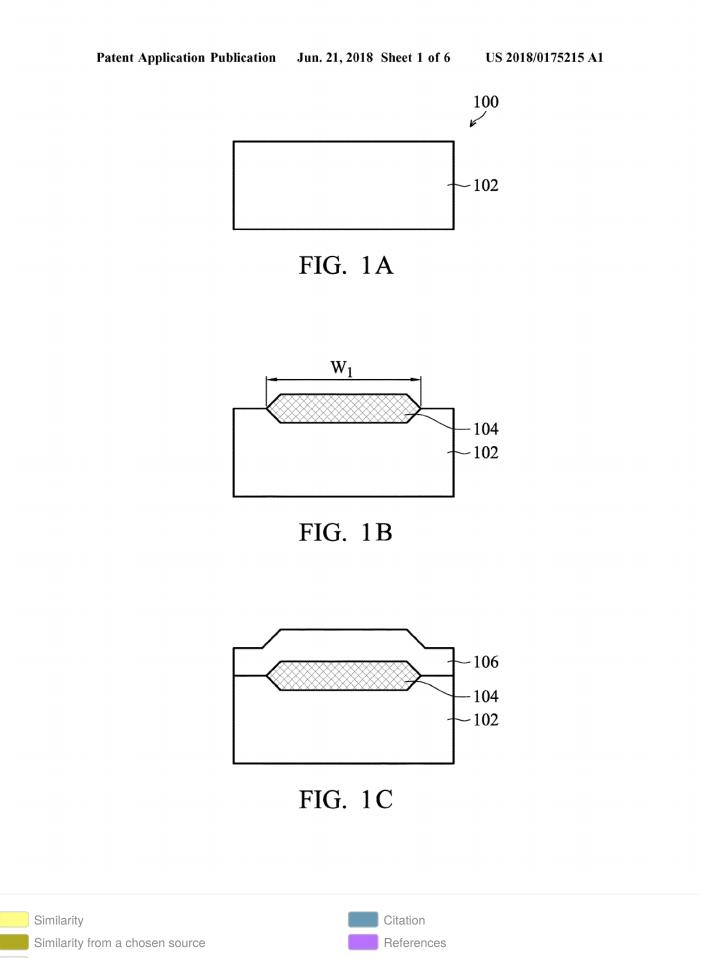

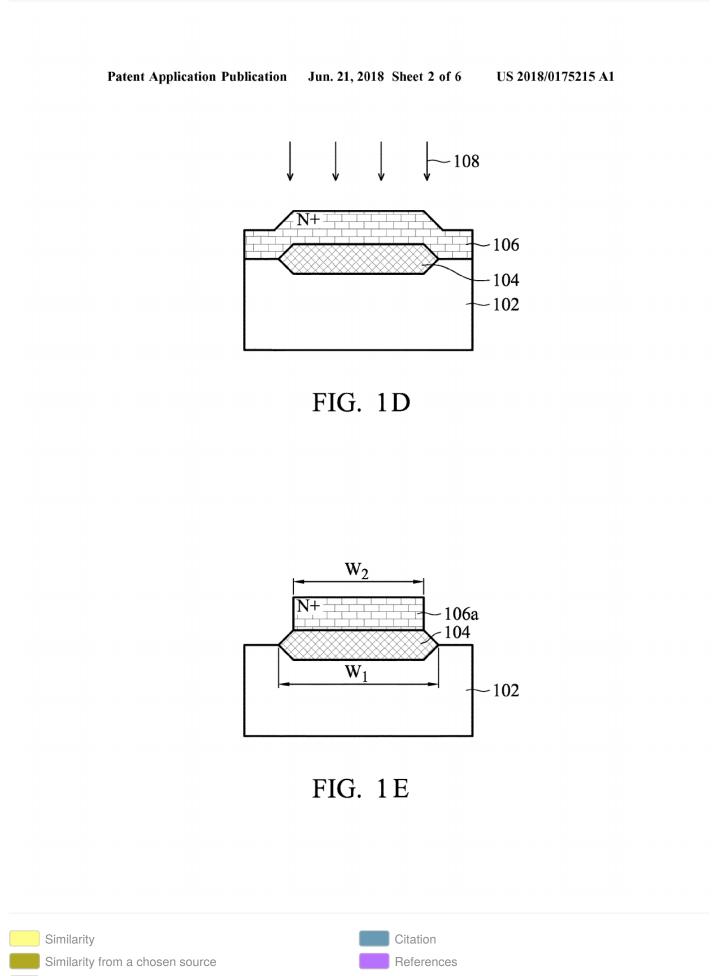

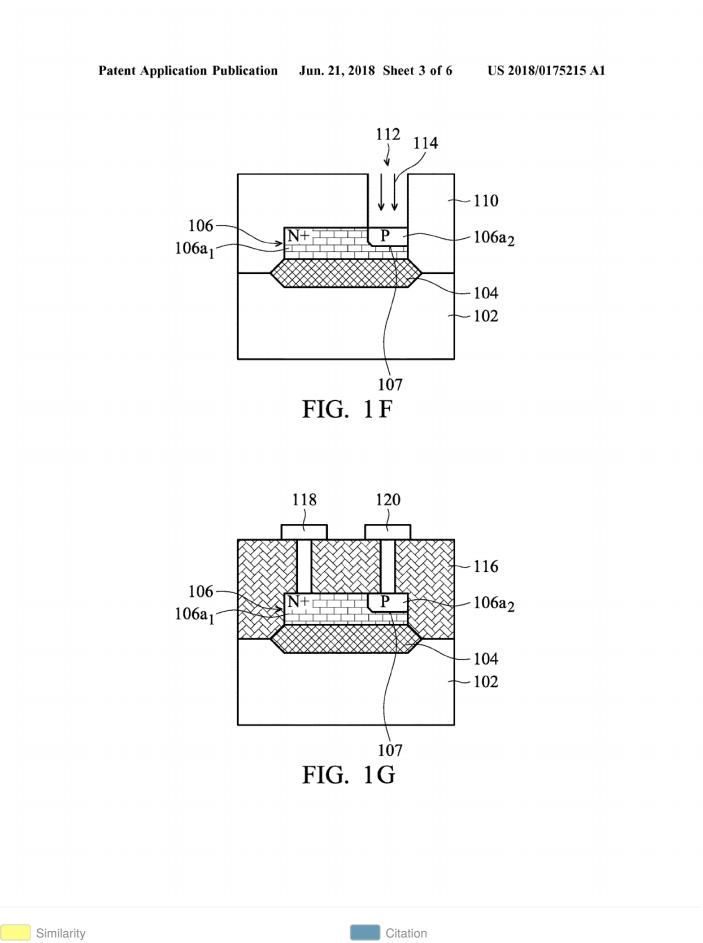

[0005] FIGS. 1A-1G illustrate cross-sectional views of a semiconductor device containing a sener divde at various stages of the manufacturing process, in accordance with some embodiments.

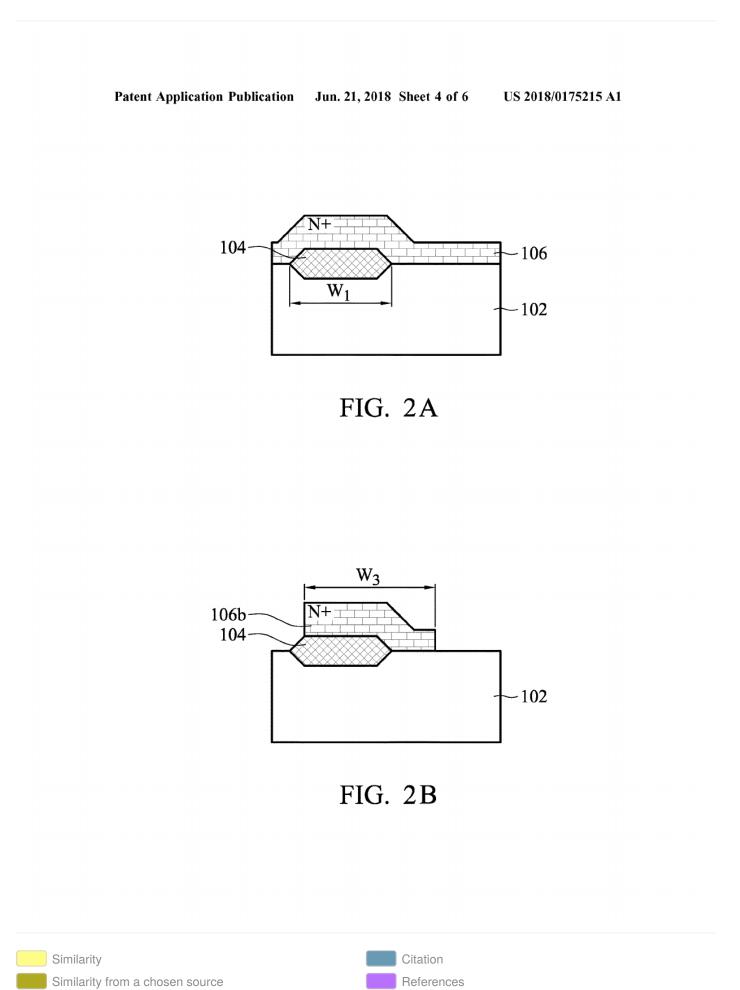

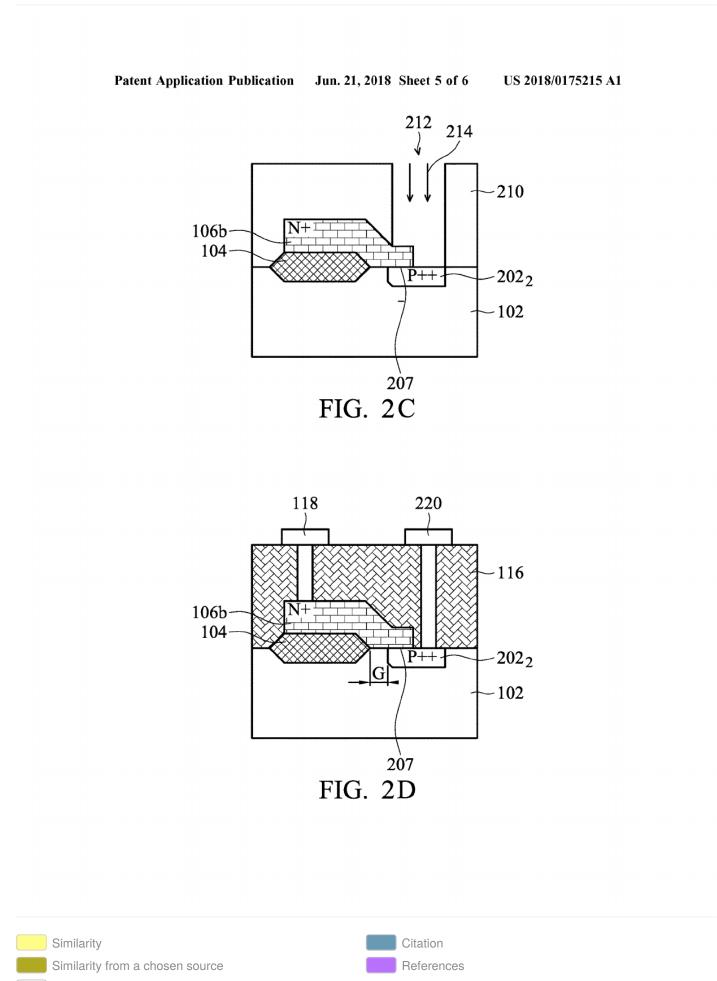

[0006] FIGS. 2A-D illustrate cross- sectional views of semiconductor device at various stages of the manufacturing process, in accordance with some embodiments.

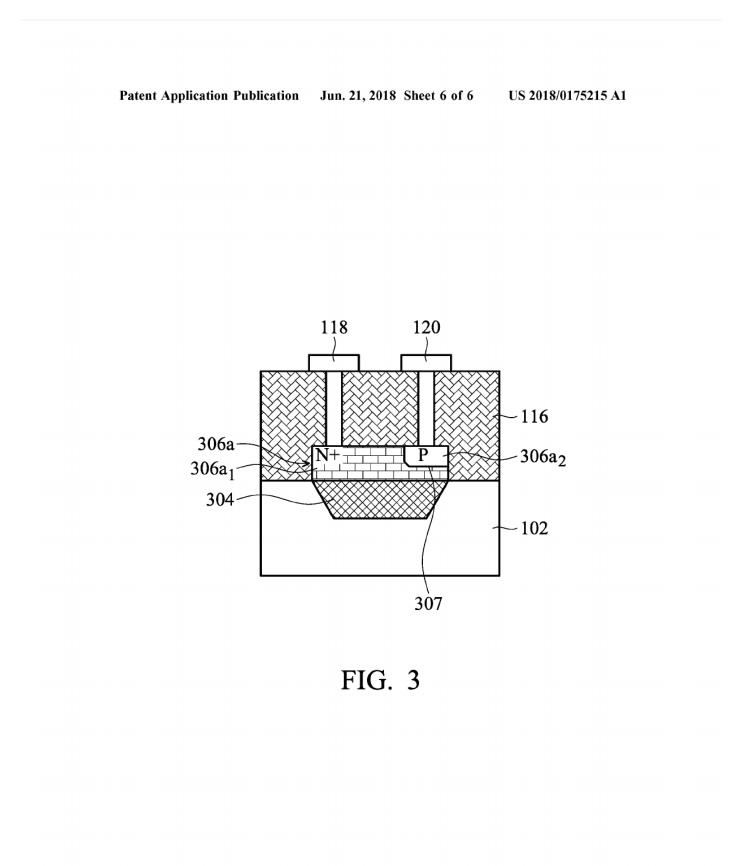

[0007] FIGS 3 illustrate a cross sectional view of a semi-conductor device in accordance with some embodiments.

#### SUMMARY

[0008] An exemplary embodiment of the present disclosure provides a semiconductor device. The semiconductor device includes an insulator formed on a top surface of a senticonductor substanc. The senticonductor device also includes a sumiconductor layer, which contains a first region for a first conductivity type and is formed on the insulator layer. The first region is a P+ region or an N+ region and has a volume of over 50-80% of that of the semiconductor layer. The semiconductor device further includes a second region of a second conductivity type in direct contact with the first region, forming a P-N junction with the first region. In

addition, the semiconductor device includes a first metallization region in electrical contact with the first region and a second metallization region in electrical contact with the second region.

[0009] An exemplary embodiment of the present disclosure provides amethod formanufacturing a semiconductor device. The method includes forming an insulator on a semiconductor substrate. The method also includes depose ting a semiconductor layer over the insulator and the semiconductor substrate. The method further includes per forming a first implantation process on the semiconductor lawer to give it a first conductivity type. In addition, the method includes patterning the semiconductor layer such that the semiconductor layer is isolated with the semiconductor substrate by the insulator. The nethod further includes forming a photoresist layer over the semiconductor substrate, and the photoresist layer has an opening exposing a motion of the insulator. a portion of the semiconductor layer. The neethod further includes performing a second inplantation process on the exposed particle of the semiconductor layer through the opening, to form a region of a second conductivity type in the semiconductor layer.

sure provides amethod formanufacturing a semiconductor device. The method 'includes forming: an insulator on a semiconductor substante. The method also includes depose iting a semiconductor layer over the insulator and the semiconductor substante. The method further includes performing a first implantation process on the semiconductor haver to give it a first conductivity type. In addition, the method includes patterning the semiconductor layer such that the semiconductor layer is partially located on the insulator and has an extension portion in direct contact with the semiconductor layer. The method includes forming a photoresist layer over the semiconductor substrate. The pitotreesist layer has an opening exposing a portion of extension portion of the semiconductor layer and a portion of the seniconductor substrate. The neethod further includes performing a second implementation process on the semicconductor substrate, through the opening, to form a region of a second conductivity type in the semiconductor substrate. The region of the second conductivity type is partially covered by the semiconductor layer.

#### DETAILED DESCRIPTION

[9911] The making and using of the embodiments of the disclosure are discussed in detail below. It should be appre-riated, however, that the embodiments can be embodied in a wide variety of specific contexts. The specific embodi ments discussed aremerely illustrative, and do not limit the Scope of the disclosure. [0012] It is to be understood that the following disclosure

nrovides many different embodiments, or examples Ufor implementing different features of the disclosure, Specific examples of components and arrangements are described below to simplify the present disclosure. These are, of course, merely examples and are not intended to belimiting. Moreover, the performance of a first process before a second process in the description that follows may include embodi ments in which the second process is performed immediately after the first process, and may also include embodi ments in which additional processes may be performed between the dirst and second processes. Various featuresmax be arbitrarily drawn in different scales for the sake of

Similarity

Similarity from a chosen source

**abc** Possible character replacement

References

#### US 2018/0175215 A1

simplicity and clarity. Furthermore, the 'formation of a 'first feature over or on a second feature in the description may include embodiments in which the first and second 'features are 'formed in direct or indirect contact.

2

10013] Some variations of the embodiments are described. Throughout the various views and illustrative embodiments. Like reference numbers are used to designate like elements. It is understood that additional steps can be provided before. during, and after the method, and some of the steps described can be replaced or eliminated "for other tembodiments of the method.

[0014] FIGS. 1A-1G illustrate cross-sectional views of a semiconductor device containing a zener diode at various stages of the nanufacturing process, in accordance with some embodiments. Referring to FIG. 1A, the semiconductor substrate 102. The semiconductor substrate 102. The semiconductor substrate 102. The semiconductor substrate 102 may be a silicon substrate 102 may be a silicon substrate 102 could be another suitable semiconductor substrate 102 may be a silicon substrate doped with a N - type substrate. In which case the substrate is an N-type substrate. The semiconductor substrate 102 may include other elementary semiconductor substrate 102 may optionally include a compound substrate 102 may include an epitaxial layer (epi layer), being strained for performance venhancement, and may include a silicon of the substrate 102 may include a solicon substrate 102 may include a silicon substrate semiconductor substrate 102 may include a silicon substrate 102 may include a silicon substrate semiconductor substrate 102 may include a compound substrate substrate 102 may include a compound substrate silicon on - insulator (SOII structure).

(0015) Referring to FIG. 1B, an insulator 104 is formed on a top surface of the semiconductor substate 102. The insulator 104 maay have a first width  $W_n$  ranging from about 1 µm to about 20 µm. In some embodiments, the insulator 104 includes a local exidation of silicon (LOCOS) structure, other suitable isolation structures, or a combination thereof. The insulator 104 may have a top surface that is higher than a top surface of the semiconductor substrate 102. In some embodiments, the insulator 104 includes silicon exide, silicon mitride, silicon extra to a surface that is higher than a top surface of the semiconductor substrate 102. In some embodiments, the insulator 104 includes silicon exide, silicon mitride, silicon extrintice, fluoridedoed silicate class (FSG ), a low -K edielectric materia, other suitable materials, or a combination thereof. In some embodiments, the first lator 104 is formed by thermal-growing an exide material through on the semiconductor substrate 102:

10016) Referring to FIG. IC, a semiconductor layer 10% is deposited over the insulator 104. In some embodinents, the semiconductor layer 196 includes silicon, either in polycrystalline or amorphous form. In alternative embodiments, the semiconductor layer 106 includes GaN, GaNs or other suitable III-V semiconductor natedrials (i.e., comprising a combination of one ormore group III elements with one or more group V elements). The III-V semiconductormaterials are particularly suitable for high-power devices because they have better thermal conductivity and can sustain higher temperature than silicon can. In some embodiments, the semiconductor layer 106 has a thickness of about 2000 anastroms to about 15000 anastroms.

[0017] Referring to FIG. 1D, a first implantation process 108 is performed on the semiconductor layer 106 such that the semiconductor layer 106 has a first conductivity type, such as an N-type or a P-type. After performing the first implantation process 108, the semicondictor layer 106 may have a heavy disping concentration, such as in a range from

#### Jun. 21, 2018

about 5e13 atoms/cm<sup>2</sup> to about 5e15 atoms/cm<sup>2</sup>. In some embodiments, in the first implantation process 10%, the semiconductor layer 106 is entirely implanted without using a mask (e.g., photoresist). In some embodiments, the first implantation process 108 uses an ion energy ranging from about 5 KeV to about 250 KeV. For the sake of illustration, an N+ semiconductor layer 106 is shown in FIG. 1D although itmayibe also formed as a P+ semiconductor layer, [0018] Afterwards, referring to FIG. 1E, the semiconductor layer 106 is patterned to a semiconductor layer 106 sthat has a second width W2 smaller than the first width W<sub>1</sub> of the insulator 104. The second width W<sub>2</sub> may be in a range from about 1  $\mu$ m to about 18  $\mu$ m. In some embodiments, the semiconductor layer 106a is disposed on the insulator 104 and physically and electrically isolated with the semiconductor ductor substrate 102 by the insulator 104.

[0019] Afterwards, referring to FIG. 1F, a patterned photoresist layer 110 is formed over the semiconductor substrate 102. The patterned photoresist layer 110 has an opening 112 exposing a portion of the semiconductor layer 106*a*. The exposed partion of the semiconductor layer 106*a*. A second implantation process 114 is performed on the exposed portion of the semiconductor layer 106 has a second implantation process 114 is performed on the exposed portion of the semiconductor layer 106 through the opening 112. The second implantation process 114 implants dopants of a second conductivity type into the exposed portion of the semiconductor layer 106*a*. The second conductivity type is opposite to the first conductivity type. For example, the second conductivity type is P-type when the first conductivity type is N-type, or vice versa. The patterned photoesist layer 110 may be removed after the second implantation process 114 is done.

100201 After performing the second implatation process 114, the semiscaduator layer 106e contains a first region 106 y of the first conductivity type and a second region 106 a of the second conductivity type. In some embodi-In the second region  $106a_2$  has a doping concentration lighter than that of the first region  $106a_1$ . For example, the second region  $106a_2$  may have a doping concentration ranging from about le13 atoms/cm<sup>2</sup> to about le15 atoms/  $cm^2$ . In some embodiments, the first region 106a<sub>1</sub> of the first conductivity type has a volume of over 50-80% of the volume of the semiconductor layer 196a while the second region 106g, occupies the remaining volume of the semi-conductor layer 106g. The second region 106g, is partially or entirely surrounded by the first region 106g, The first and second regions  $106a_1$  and  $106a_2$  of the semiconductor layer 196a are in direct contact with each other and form a P-N investion 107. The first and second regions  $106a_{\mu}$  and  $106a_{\tau}$  of the seniiconductor layer  $106a_{\tau}$  may function as a zener diode. This kind of device is used in triuming circuits and in particular a zener-like triunning device. In some embodiments, the depth of the second region  $106a_2$  of the semiconductor layer 106a is substantially the same as or less than of the thickness of the semiconductor layer 106a. For the sake of illustration, a P region  $106u_2$  is shown in FIG. IF although it may be also formed as an N region,

[0021] Afterwards, referring to FIG. 1G, an inter-layer dielectric (ILD) layer 116 is formed over the semiconductor substrate 102. A first needallization contact 118 and a second metallization contact 120 are formed through the LD layer 116 to be in electrical contact with the first region 106 $a_1$  and the second region 106 $a_2$  of the semiconductor layer 106a, respectively. In some embodiments, the ILD layer 116

Similarity

#### US 2018/0175215 A1

3

includes a low-k dielectric natterial, silicon oxide layer or a combination thereof. The low-k dielectric material has a dielectric constant less than about 3.0. A wirk variety of low-k dielectric natterials may be employed to from the low-k dielectric layer, including fluorinated silicon plass (FSG), carbon doped silicon oxide. Black diamond® (Apo nlied Materials of Santa Clara, Calif. L Xerogel. Aerogel, amorphous fluorinated carbon, Parylene, BCB (bis-bertao cyclobutenes), SILK (Dow Chemical, Midland, Mich.), polyimide, and/or other future developed low-k dielectric instorials. In some entbodiments, the HLD layer 116 is formed by chemical vapor deposition (CVD), spin-on coating or other suitable techniques. In some entbodiments, the first and second metablization contacts 118 and 120 are formed of a metal, which may be titanium, titanium nitride, ungsten, aluminum, tantalum, titunium nitride, or a combination thereof.

nation thereof. [0022] The semiconductor device 100 containing a zener diode can be manufactured easily. For example, the semiconductor layer 106*a* includes only two regions 106*a*1 and  $106a_2$  (e.g., the P regions and the N+ region as shown in FIG- 16). The semiconductor layer 106*a* does not include a third region other than the first and second regions 106*a*, and 106*a*2. Accordingly, during the process of mainfacturing the zener diode, only two implantation processes 108 and 114 are needed to be performed on the semiconductor layer 1066, and only onemask (e.g., the photoresits layer 110) is needed in these two implantation processes 108 and 114.

10023] FIGS. 2A-D illustrate pross-sectional views of a semiconductor device at various stages of manufacturing processes, in accordance with some embodiments. Referring to FIG, 2A, a semiconductor device 200 similar to the semiconductor device 100 as shown in FIG. 1D is provided, including the semiconductor layer 106 of the first conductivity type. In some embodiments, the insulator 104 has the first with  $W_{1}$ .

[0024] Afterwards, referring to FIG. 2B, the semiconductor layer 106 is patterned to a semiconductor layer 106b that has a third width  $W_3$  which is greater than the first width  $W_1$  of the insulator 104. The third width W3 of the semicoon ductor layer 106b may be in a range from about 2 µm to about 25 µm. Abcordingly, the semiconductor layer 106b has an extension portion that extends over a sidewall of the insulator 104 and is in direct contact with the semiconductor substrate 102.

[0025] Afterwards, referring to FIG. 2C, a patterned photoresist layer 210, which is formed over the semiconductor substrate 102, has an opening 212 exposing at least a portion of the semiconductor layer 106b and a portion of the semiconductor substrate 102 adjacent to the semiconductor layer 106b. In some embodiments, the opening 212 also exposes a sitewall of semiconductor layer 106b.

[0026] A second implantation process 214 is then performed on the semiconductor substrate 102 through the opening 212. The second implantation process 214 implants dogants of the second conductivity type into the semiconductor substrate 102. A region 202, of the second conductivity type is formed in the semiconductor substrate 102, near the top surface of the semiconductor substrate 102. The second region 2022 is partially covered by (i.e., under) the semiconductor layer 1966. In some eniboliments, the second region 2022 has a doping concentration heavier than that

#### Jun. 21, 2018

of the semiconductor layer 106b. For example, the region 2022 may have a doping concentration ranging from about 5e13 atoms/cm<sup>2</sup> to about 8e15 atoms/cm<sup>2</sup>. In some embodiments, the second implantation process 214 uses an ion energy ranging from about 5 KeV to about 2000 KeV, such that the dopints many paretuate the semiconductor layer 106b to reach the semiconductor substrate 102 and forms the second region 202<sub>2</sub> near the top surface of the semiconductor substrate 102. An annealing process may be performed after the second implantation process. The patterned photoresis layer 210 may be removed after the second implantation process 214 uses 106b and the region 202<sub>2</sub> may form a P-N junction 207 and function as a zener diode. For the sake of illustration, a P++ region 2022 is shown in FIGO. 2C although it may be also formed as an N++ region.

[0027] Afterwards, referring to FIG. 2D, the inter-layer dielectric (IILD) layer 116 is formed over the semiconductor substrate 102 and the patterned semiconductor layer 106b. The first netablization contact 118 is formed through the LD layer 116 to be in electrical contact with the semiconductor dayer 106b. A second metablization contact 220 is formed through the ILD layer 116 to be in electrical contact with the semiconductor layer 106b. The second metablization contact 220 is formed through the ILD layer 116 to in electrical contact a portion of the second region 202<sub>2</sub> that is not covered by the semiconductor layer 106b. The second metablization contact 220 does not penetrate the semiconductor layer 106b but has a horizontal gap G' between itself and the semiconductor layer 106b. Therbornicating ap G' many be in a range from 0.5 put no about 7  $\mu$ m. Furthermore, there is a horizontal gap 22<sub>1</sub> as shown in FIG. 2D.

shown in FIG. 2D: [0028] The semiconductor device 200 centraining a zener diode can be easily manufactured. For example, during the processes of manufacturing the zener diode, only two implantation processes 108 and 214 are needed to be performed on the semiconductor layer 1066, and only one mask (e.g., the patterned photoassist layer 210) is needed in these two implantation processes 108 and 214.

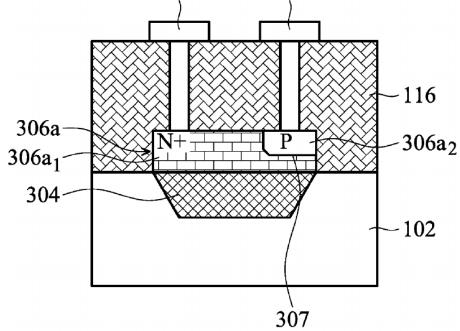

[0029] FIGS. 3 illustrate a cross-sectional view of a semiconductor device in accordance with some embodiments. A semiconductor device 300 that is similar to the semiconductor device 100, except that the insulator 304 is an STI structure, is provided. The formation of the isolation structure 304 includes patterning the semiconductor substrate 100 by a bhotolithography process, etching a recess, such as a trench, in the semiconductor substrate 102 (for example, by using a dry etching, wet etching, other applicable etching processes or a combination thereof), and filling the recess (for example, by using chemical vapor deposition).

[0030] The insulator 304 may have the first width  $W_1$ . The insulator 304 may have a top surface level with that of the semiconductor substrate 102. The semiconductor substrate 102 may provide a flat surface for forming the semiconductor to layer 306a on it. The semiconductor layer 306a may be made of the same material and by the same formation method as the semiconductor layer 106a described above. The semiconductor layer 306a may have the second region 306a<sub>2</sub> is located in the semiconductor layer, although the semiconductor layer 306a may have the third width W2 while the second region 306a<sub>2</sub> is located in the semiconductor substrate. The semiconductor layer 306a may have the third width W2 while the second region 306a<sub>2</sub> is located in the semiconductor substrate. The first region 306a<sub>1</sub> and the semiconductor substrate. The first region 306a<sub>1</sub> and the second may function as a zener diode.

Similarity

#### US 2018/0175215 A1

4

[0031] Although the embodiments and their advantages have been described in detail, it should be understood that various changes, substitutions, and alterations an bemade herein without departing from the spirit and scope of the embodiments as defined by the annended claims Moreover the scope of the present application is not intended to be limited Ito Ithe Inarticular Lembodiments lof the Incoess machine.manufacture.composition ofmatter.means.meth ods and stens described in the specification As one of ordinary skill in the art will readily appreciate from the disclosure processes machines manufacture compositions of matter, means, methods, or steps, presently lexisting or laver to be developed, that perform [substantially the same function or achieve substantially the same result as the corresponding (embodiments described herein may be uti-lized according to the disclosure.Accordingly, the appended claims are lintended to include within their scope such processes, machines, manufacture, compositions ofmatter, means methods orstens [maddition each claim constitutes a separate combodiment, and the combination of various claims and embodiments are within the scope of the disclo sure.

What is claimed is:

1. A semiconductor device, comprising:

- and insulator formed on a top surface of a semiconductor substrate;

- a seniconductor layer, containing a first region of a first

- seance induction rayer, command a mist region of a mist conductivity type, formed on the insulator layer, wherein the first region is a P+ region or an N+ region; second region of a second conductivity type in direct contact with the first region, wherein the P-N junction with the first region, wherein the P-N junction com-mises a first period parallel is that for an exprane of the prises a first portion parallel to the top surface of the semiconductor substrate, and the second region is the seniconductor substrate and partially covered by the semiconductor laver:

- first metallization region in electrical contact with the a first region ; and

- a speconometallization region in electrical contact with the second region.

2. The semiconductor device as claimed in claim 1, wherein the semiconductor layer lays an extension portion extending over a sidewall of the insulator and in direct contact with the semiconductor substrate.

3. The semiconductor device as claimed in claim 1, wherein the second metallization contact is not covered by the with a portion of the second region that is not covered by the semiconductor layer.

4. The semiconductor device as claimed in claim wherein the second<sup>1</sup> meterialization contact has a horizontal gap with the samiconductor layer.

5. The semiconductor device as claimed in claim 1, where in the semiconductor layer comprises silicon.

6. The semiconductor device as claimed in claim 1, wherein the semiconductor layer comprises Gan, Gans or other III-V semiconductor materials.

The semiconductor device as claimed in claim 1, wherein the insulator comprises a local oxidation of silicon structure.

semiconductor device as claimed in claim 1, The wherein the insulator comprises a shallow trench isolation structure.

Jun. 21, 2018

9. The semiconductor device as claimed in claim 1, wherein a first top surface of the insulator is higher than a second top surface of the semiconductor substrate.

10. The semiconductor device as claimed in claim  $1_1$  wherein a thickness of the semiconductor layer is about 2000 angstroms to about 15000 angstroms.

The semiconductor device as claimed in claim 1, wherein a second width of the semiconductor layer is greater than a first width of the insulator.

12. The semiconductor device as claimed in claim 11, wherein the first width is ranging from about 1  $\mu m$  to about 20 µm, and the second width is ranging from about 2 µm to about 25 µm.

13. The seniiconductor device as claimed in claim 1, further comprising an inter-layer dielectric layer formed over the senticonductor substrate, wherein the inter-layer dielectric layer directly contacts the semiconductor substrate, the insulator, and the semiconductor layer.

14. The semiconductor device as claimed in claim herein a second doping concentration of the second region is heavier than a first doping concentration of the first region.

15. The semiconductor device as claimed in claim 14, wherein the second doping consentration is in a range from about 5e13 atoms/cm<sup>2</sup> to about 8e15 atoms/cm<sup>2</sup>

16. Amethod formanufdaturing the semiconductor device

of claim 1, comprising: forming an insulator on a semiconductor substrate;

depositing a semiconductor layer over the insulator and the semiconductor substrate;

performing a first implantation process on the semiconductor layer to give it a first conductivity type;

- patterning the semiconductor layer such that the semiconductor layer is partially located on the insulator and has an extension portion in direct contact with the semiconductor substrate;

- forming a photoresist layer over the semiconductor substrate, wherein the photoresist layer has an opening exposing a portion of extension portion of the semiconductor layer and a portion of the senticonductor substrate; and

- performing a second implantation process on the semiconductor substrate, through the ovening, to form a region of a second conductivity type in the semicomductor substrate, wherein the region of the second conductivity type is partially covered by the semiconductor layer, wherein the region of the second conductivity type in direct contact with the semiconductor layer of the first conductivity type to form a P-N junction, and wherein the P-N junction is paraillel to a top surface of the semiconductor substrate.

17, Themethod as claimed in claim 16, further comprising:

- removing the photoresist layer after performing the second implantation process;

- forming an inter-layer dielectric layer over the semiconductor substrate and the semiconductor layer:

- forming a first metablization contact and a second metablization contact in electrical contact with the semiconductor layer of the first conductivity type and the region of the second conductivity type, respectively.

18. Themethod as claimed in claim 16, wherein the second amplantation process uses an ion energy ranging from about 5 KeW to about 250 KeW,

Jun. 21, 2018

US 2018/0175215 A1

5

19. The method as claimed in claim 16, wherein the semiconductor layer is entirely implanted without using a mask in the first implantation process. 20. The method as elaimed in claim 16, wherein the opening of the photoresist layer comprises exposing a side-wall of the semiconductor layer.

\* \* \* \* \*